在英特尔和台积电之后国内平台配资,韩国芯片巨头也加入了EUV光刻机新竞赛。

三星电子半导体(DS)部门最早将于今年年底引进High NA极紫外(EUV)设备。除了下一代曝光设备之外,我们还在开发可以检查高数值孔径掩模的设备。看来他们正在积极从事技术开发,以便在与英特尔和台积电等全球半导体竞争对手的“芯片大战”中具有竞争力。

据业内人士13日报道,三星电子最早将于今年年底和明年第一季度开始进口该公司首款High NA EUV设备“EXE:5000”。据说,华城校区的半导体研究中心(NRD)被认为是第一个 Hi-NA 的可能地点。三星的第一台高数值孔径 EUV 设备预计将用于代工。

ASML生产的High NA EUV设备的第一个客户是美国英特尔。据称,继英特尔和台湾台积电之后,三星电子也将接收该设备。

ASML 生产 8台 EXE:5000。英特尔不仅拿走了第一台设备,还拿走了其他几台设备。于是,就有了这样的故事:三星是最后一个采购这一代High NA光刻机的客户。SK海力士预计将在下一个版本的EXE:5200推出以后,再将High-NA EUV引入DRAM生产。

High NA EUV设备每台成本为四亿美金。而且它非常大。然而,由于它是处理 13.5nm 波长的设备,因此非常敏感且要求较高。即使今年年底开始引进设备,也需要相当长的时间来哄设备并完美安装,预计该设备投入晶圆的时间将在明年上半年左右。

预计三星在完成高数值孔径 EUV 设备的安装后将开始构建成熟的生态系统。有关此项建设工作的线索是从12日在京畿道水原市水原会议中心举行的“2024光刻+图案化会议”中获得的。

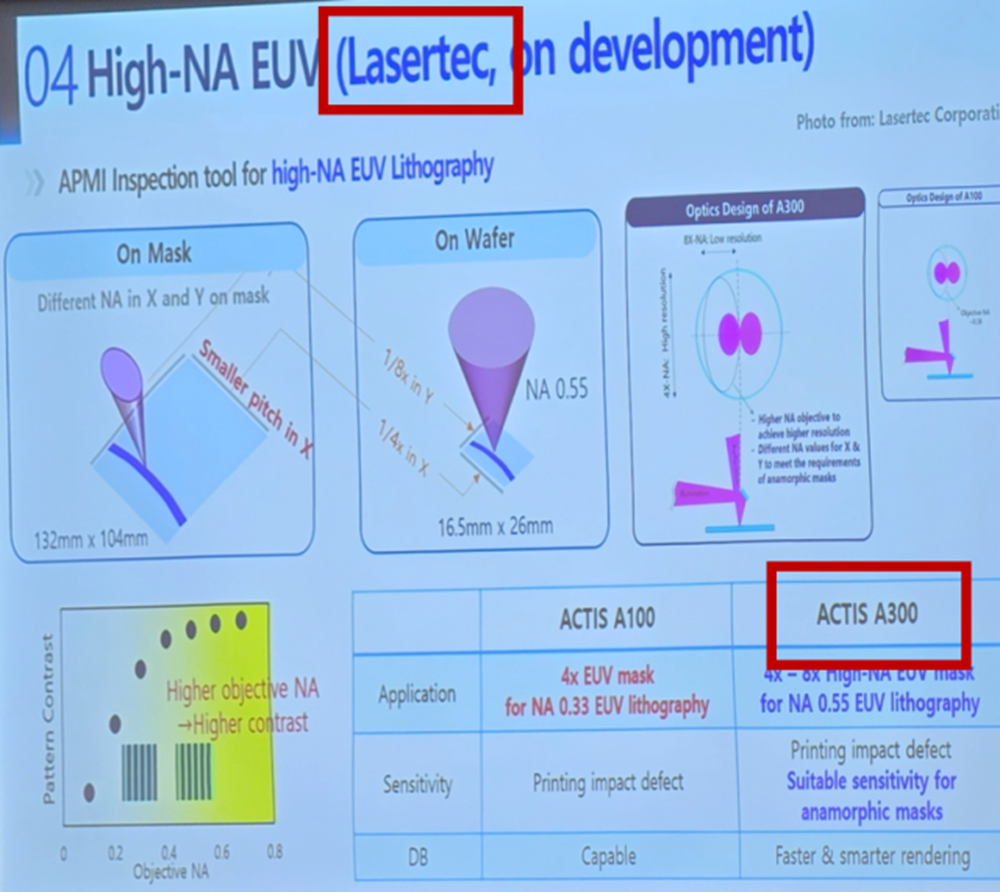

在这次会议上,三星电子半导体研究所开发光掩模的Min Cheol-ki博士做了演讲。在本次演讲中,Min博士提到了用High NA EUV的掩模检测设备(APMI)。

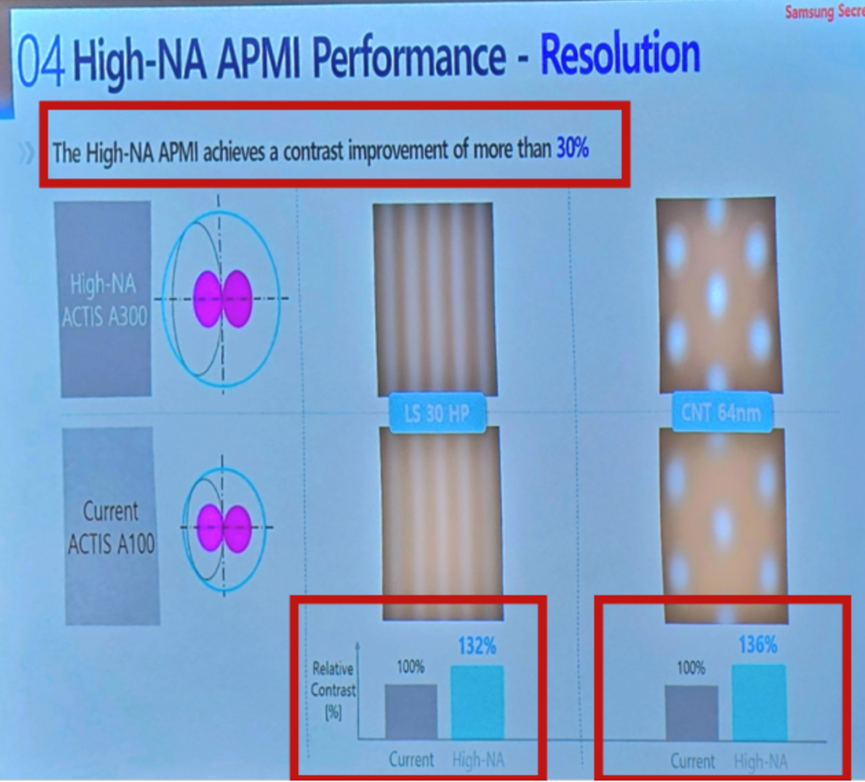

闵博士宣布正在与日本Lasertech合作开发High NA掩模检测设备。Min博士解释说:“当我们使用High NA EUV检查半导体掩模时,与现有EUV相比,对比度提高了30%以上。”从现在起,我们将仔细审视这一说法。

让我简单地解释一下,从mask和检测设备开始。掩模是进入ASML曝光机的材料。为了让 EUV 光捕获晶圆上要雕刻的电路,它必须接触掩模并穿过它。

曝光设备中使用的掩模是在称为掩模车间的地方制造的。要印刷在晶圆上的电路被雕刻在透明的空白掩模上。然而,EUV掩模版的价格相当昂贵。光掩模的形状为6英寸×15厘米,但价格昂贵,每片售价1亿韩元。我们可以通过定期检查一次性正确制作这些“很棒”的mask,从而降低生产成本。只有在曝光机中很好地刻出电路,才能将晶圆缺陷降至最低。因此,掩模版检测设备的性能在整个曝光过程中非常重要。

Min 博士宣布,他正在与 Lasertech 合作研究这种设备,也称为“APMI”,用于高数值孔径 EUV 。光化图案掩模检测 (APMI)。简而言之,它是使用波长为13.5 nm的EUV光源来检查掩模的设备。尽管略逊于ASML,Lasertech也是一家拥有强大EUV技术的设备公司。通过低数值孔径 EUV 掩模检测设备,他们的世界一流技术已获得认可。

据了解,三星电子购买了一台 Lasertech 的高数值孔径 EUV 掩模检测设备“ACTIS A300”。预计今年上半年后将开始全面导入,届时ASML的EXE:5000将安装在三星电子内部。

不过,Min博士在介绍High-NA面膜时并不仅仅提到了Lasertech,他们还宣布正在与一家自动化设计工具(EDA)公司合作设计一种新型掩模。在High NA EUV中,正在考虑将掩模电路绘制为曲线(曲线)而不是直线的方法,以便更清晰地将电路印刷在晶圆上。Min 博士还解释说,他正在与全球半导体 EDA 工具公司 Synopsys 合作开展这项工作。除了 ASML、Lasertech 和 Synopsys 之外。预计三星将与多家公司一起为 High-NA 时代做准备,其中包括 JSR 等光刻胶公司和在晶圆上应用光刻胶的设备公司 Tokyo Electron。三星电子正通过这一生态系统建设工作,为 2027 年 Hi-NA 的全面商业化做准备。

近两年来,2.5D封装和HBM问题一直受到媒体和行业的关注。三星电子于2019年在全球首次推出使用EUV生产的芯片,如今又向前迈进了一步,即将进入High-NA时代。如何封装堆叠一个完整的DRAM或系统半导体是一个重要的问题,但如何在整个工艺上制作出更精细、完整度更高的电路也是一个非常重要的根本问题。

SK海力士,2026年入局

SK海力士正在加速开发用于尖端存储器的High NA EUV技术。公司首个High NA EUV设施计划于2026年从ASML引进,据悉目前正在全力建立新的研发团队并扩充人员。

16日业内人士透露,SK海力士计划在2026年推出应用High NA EUV设备。

出席12日举行的“下一代光刻+图案化”会议的SK海力士EUV材料技术负责人在接受记者采访时表示,“计划于2026年引进高NA EUV设备”,并表示:“目前,该公司没有High NA EUV开发人员。“这种情况正变得越来越普遍,”他解释道。

SK海力士还计划在2026年引进一个设备,并积极进行High NA EUV的研发。虽然具体计划,如晶圆厂引进设备或追加投资方向等尚未透露,但预计最早可应用于0a(个位数纳米级DRAM)量产。

与此相关国内平台配资,SK海力士去年底成立了一个单独的团队来开发High-NA EUV技术。此前,公司内部有一个组织全面开发EUV和High-NA EUV,但这被解读为通过细分来强化专业知识的策略。